TSMC (Taiwan semiconductor) has a major multi-year plan to create giant rectangular substrate (510 millimeters by 515 millimeters —about 20 inches by 20 inches) with over triple the usable area of current round wafers.</a> The rectangular shape means there would also be less unused area left over at the edges. this means less waste because of the rectangular shape and lower costs and higher volume by tripling the size.

The idea behind the new approach is to use rectangular panel-like substrates, rather than the conventional round wafers used today, allowing more sets of chips to be placed on each wafer.

The study is still in its early stages, but it represents a significant technical shift by TSMC, which previously viewed the use of rectangular substrates as too challenging. To make the new method work, TSMC and its suppliers would have to devote a significant amount of time and effort to development as well as upgrade or replace numerous production tools and materials.

TSMC's advanced chip stacking and assembly techniques -- used to produce AI chips for Nvidia, AMD, Amazon and Google -- employ 12-inch silicon wafers, the largest available. The chipmaker is expanding its advanced chip packaging capacity in Taiwan to keep up with runaway demand. The expansion in Taichung is mainly for Nvidia, sources briefed on the matter said, while its Tainan expansion is for Amazon and Amazon's chip design partner Alchip.

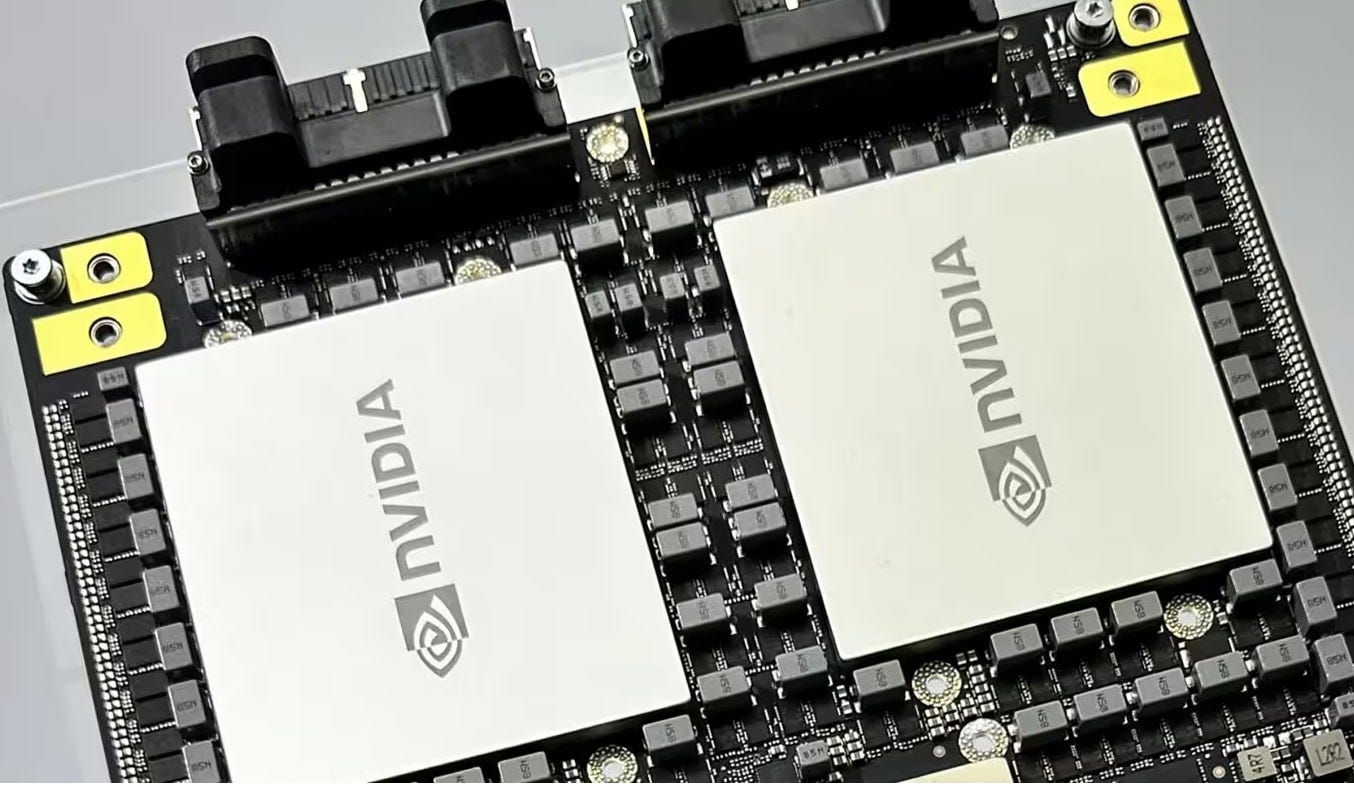

For AI computing chips like Nvidia's H200 and B200, using state-of-the-art chip production alone is not enough. Advanced chip packaging technology called CoWoS, chip-on-wafer-on-substrate pioneered by TSMC, is also necessary. For B200 chipsets, for example, CoWoS makes it possible to combine two Blackwell graphic processing units and connect them with eight high bandwidth memories (HBMs), enabling fast data throughput and accelerated computing performance.

But as chip size grows to accommodate more transistors and to integrate more memory, the current industry standard -- 12-inch wafers with an area of approximately 70,685 sq. millimeters -- may not be efficient enough for packaging cutting-edge chips in a couple of years.

Keep reading with a 7-day free trial

Subscribe to next BIG future to keep reading this post and get 7 days of free access to the full post archives.